Product Datasheet Search Results:

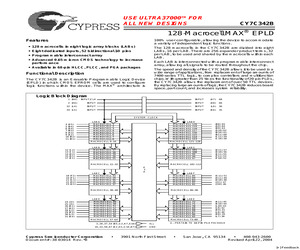

- CY7C342B15JC

- Cypress Semiconductor

- CPLD MAX® Family 2.5K Gates 128 Macro Cells 83.3MHz 0.65um (CMOS) Technology 5V 68-Pin PLCC

- CY7C342B15JC

- Cypress Semiconductor

- CPLD MAX® Family 2.5K Gates 128 Macro Cells 83.3MHz 0.65um (CMOS) Technology 5V 68-Pin PLCC

Product Details Search Results:

Cypress.com/CY7C342B15JC

{"Number of Logic Blocks/Elements":"8","Mounting":"Surface Mount","Number of Usable Gates":"2500","Programmable":"Yes","Operating Temperature (Min)":"0C","Operating Temperature (Max)":"70C","Operating Temperature Classification":"Commercial","Package Type":"PLCC","# Macrocells":"128","Operating Supply Voltage (Max)":"5.25 V","Propagation Delay Time":"15 ns","Family Name":"MAX\ufffd","Operating Supply Voltage (Min)":"4.75 V","Frequency (Max)":"100 MHz","Operating Temp Range":"0C to 70C","Pin Count":"68","# I...

1738 Bytes - 11:41:37, 17 November 2024

Documentation and Support

Use our online request for specific proposed solutions or send your technical question directly to a product specialist at request:

| File Name | File Size (MB) | Document | MOQ | Support |

|---|---|---|---|---|

| 8538SBG13V06CY74.pdf | 2.13 | 1 | Request |