Did you mean: XC3020-100CB100B

Product Datasheet Search Results:

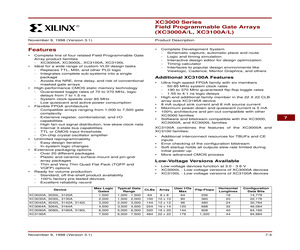

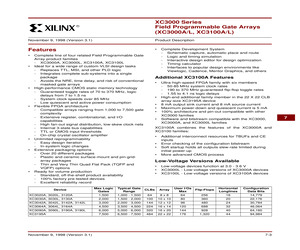

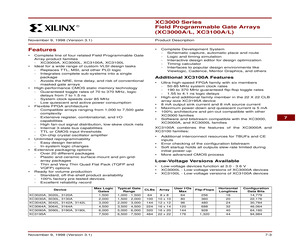

- XC3020-100CB100B

- Xilinx, Inc.

- FPGA: XC3000 Family: SRAM Switch Tech.: Reprogrammable: 256 Logic Cells: 256 Reg.: 5V Supply: 100 Speed Grade: 100QFP

- XC3020-100CB100C

- Xilinx, Inc.

- FPGA: XC3000 Family: SRAM Switch Tech.: Reprogrammable: 256 Logic Cells: 256 Reg.: 5V Supply: 100 Speed Grade: 100QFP

- XC3020-100CB100M

- Xilinx, Inc.

- FPGA: XC3000 Family: SRAM Switch Tech.: Reprogrammable: 256 Logic Cells: 256 Reg.: 5V Supply: 100 Speed Grade: 100QFP

- XC3020-100CBG100B

- Xilinx, Inc.

- FPGA: XC3000 Family: SRAM Switch Tech.: Reprogrammable: 256 Logic Cells: 256 Reg.: 5V Supply: 100 Speed Grade: 100QFP

- XC3020-100CB100B

- Xilinx, Inc.

- FPGA: XC3000 Family: SRAM Switch Tech.: Reprogrammable: 256 Logic Cells: 256 Reg.: 5V Supply: 100 Speed Grade: 100QFP

- XC3020-100CB100C

- Xilinx, Inc.

- FPGA: XC3000 Family: SRAM Switch Tech.: Reprogrammable: 256 Logic Cells: 256 Reg.: 5V Supply: 100 Speed Grade: 100QFP

- XC3020-100CB100M

- Xilinx, Inc.

- FPGA: XC3000 Family: SRAM Switch Tech.: Reprogrammable: 256 Logic Cells: 256 Reg.: 5V Supply: 100 Speed Grade: 100QFP

Product Details Search Results:

Xilinx.com/XC3020-100CB100B

{"VIH Min. (CMOS) (V)":"3.5","V(OL)Max.(V)Lo Level Out.Volt.":"0.4","Digital Input V Max (V)":"7.5","Vsup(+) Nom.(V) Pos.Sup.Volt.":"5.0","Quiescent Current Max (TTL)":"15m","Pins":"100","@Iol (A)":"4.0m","Logic Level Family":"CMOS and T","Quiescent Current Max (CMOS)":"1m","Package Body Material":"Ceramic","Gate Capacity":"2000","VIL Max. (TTL) (V)":"0.8","Package":"QFP","VIH Min. (TTL) (V)":"2.0","@IOH (test)":"4.0m","Configurable Logic Blocks":"64","VIL Max. (CMOS) (V)":"1.0","Military":"N","Mil Number":...

1258 Bytes - 16:35:28, 16 November 2024

Xilinx.com/XC3020-100CB100B(SMD)

{"VIH Min. (CMOS) (V)":"3.5","V(OL)Max.(V)Lo Level Out.Volt.":"0.4","Digital Input V Max (V)":"7.5","Vsup(+) Nom.(V) Pos.Sup.Volt.":"5.0","Quiescent Current Max (TTL)":"15m","Pins":"N/A","@Iol (A)":"4.0m","Logic Level Family":"CMOS and T","Quiescent Current Max (CMOS)":"1m","Package Body Material":"Ceramic","Gate Capacity":"2000","VIL Max. (TTL) (V)":"0.8","Package":"QFP","VIH Min. (TTL) (V)":"2.0","@IOH (test)":"4.0m","Configurable Logic Blocks":"64","VIL Max. (CMOS) (V)":"1.0","Military":"Y","Mil Number":...

1289 Bytes - 16:35:28, 16 November 2024

Xilinx.com/XC3020-100CB100C

{"VIH Min. (CMOS) (V)":"3.5","V(OL)Max.(V)Lo Level Out.Volt.":"0.4","Digital Input V Max (V)":"7.5","Vsup(+) Nom.(V) Pos.Sup.Volt.":"5.0","Quiescent Current Max (TTL)":"10m","Pins":"100","@Iol (A)":"4m","Logic Level Family":"CMOS and T","Quiescent Current Max (CMOS)":"500u","Package Body Material":"Ceramic","Gate Capacity":"2000","VIL Max. (TTL) (V)":"0.8","Package":"QFP","VIH Min. (TTL) (V)":"2.0","@IOH (test)":"4m","Configurable Logic Blocks":"64","VIL Max. (CMOS) (V)":"1.0","Military":"N","Number of User...

1227 Bytes - 16:35:28, 16 November 2024

Xilinx.com/XC3020-100CB100M

{"VIH Min. (CMOS) (V)":"3.5","V(OL)Max.(V)Lo Level Out.Volt.":"0.4","Digital Input V Max (V)":"7.5","Vsup(+) Nom.(V) Pos.Sup.Volt.":"5.0","Quiescent Current Max (TTL)":"10m","Pins":"100","@Iol (A)":"4m","Logic Level Family":"CMOS and T","Quiescent Current Max (CMOS)":"500u","Package Body Material":"Ceramic","Gate Capacity":"2000","VIL Max. (TTL) (V)":"0.8","Package":"QFP","VIH Min. (TTL) (V)":"2.0","Configurable Logic Blocks":"64","VIL Max. (CMOS) (V)":"1.0","Military":"N","Number of User I/Os":"64","Vsup (...

1168 Bytes - 16:35:28, 16 November 2024

Xilinx.com/XC3090-100CB164B

{"VIH Min. (CMOS) (V)":"3.5","V(OL)Max.(V)Lo Level Out.Volt.":"0.4","Digital Input V Max (V)":"7.5","Vsup(+) Nom.(V) Pos.Sup.Volt.":"5","Quiescent Current Max (TTL)":"15m","Pins":"N/A","@Iol (A)":"4.0m","Logic Level Family":"CMOS and T","Quiescent Current Max (CMOS)":"3m","Package Body Material":"Ceramic","Gate Capacity":"9000","VIL Max. (TTL) (V)":"0.8","Package":"QFP","VIH Min. (TTL) (V)":"2.0","@IOH (test)":"4m","Configurable Logic Blocks":"320","VIL Max. (CMOS) (V)":"1.0","Military":"N","Mil Number":"59...

1229 Bytes - 16:35:28, 16 November 2024

Xilinx.com/XC3090-100CB164B(SMD)

{"VIH Min. (CMOS) (V)":"3.5","V(OL)Max.(V)Lo Level Out.Volt.":"0.4","Digital Input V Max (V)":"7.5","Vsup(+) Nom.(V) Pos.Sup.Volt.":"5","Quiescent Current Max (TTL)":"15m","Pins":"N/A","@Iol (A)":"4.0m","Logic Level Family":"CMOS and T","Quiescent Current Max (CMOS)":"3m","Package Body Material":"Ceramic","Gate Capacity":"9000","VIL Max. (TTL) (V)":"0.8","Package":"QFP","VIH Min. (TTL) (V)":"2.0","@IOH (test)":"4m","Configurable Logic Blocks":"320","VIL Max. (CMOS) (V)":"1.0","Military":"Y","Mil Number":"59...

1258 Bytes - 16:35:28, 16 November 2024

Xilinx.com/XC3090-100CB164C

{"VIH Min. (CMOS) (V)":"3.5","V(OL)Max.(V)Lo Level Out.Volt.":"0.4","Digital Input V Max (V)":"7.5","Vsup(+) Nom.(V) Pos.Sup.Volt.":"5","Quiescent Current Max (TTL)":"10m","Pins":"N/A","@Iol (A)":"4.0m","Logic Level Family":"CMOS and T","Quiescent Current Max (CMOS)":"500u","Package Body Material":"Ceramic","Gate Capacity":"9000","VIL Max. (TTL) (V)":"0.8","Package":"QFP","VIH Min. (TTL) (V)":"2.0","@IOH (test)":"4m","Configurable Logic Blocks":"320","VIL Max. (CMOS) (V)":"1.0","Military":"N","V(OH)Min.(V)H...

1200 Bytes - 16:35:28, 16 November 2024

Xilinx.com/XC3090-100CB164M

{"VIH Min. (CMOS) (V)":"3.5","V(OL)Max.(V)Lo Level Out.Volt.":"0.4","Digital Input V Max (V)":"7.5","Vsup(+) Nom.(V) Pos.Sup.Volt.":"5","Quiescent Current Max (TTL)":"10m","Pins":"N/A","@Iol (A)":"4.0m","Logic Level Family":"CMOS and T","Quiescent Current Max (CMOS)":"500u","Package Body Material":"Ceramic","Gate Capacity":"9000","VIL Max. (TTL) (V)":"0.8","Package":"QFP","VIH Min. (TTL) (V)":"2.0","Configurable Logic Blocks":"320","VIL Max. (CMOS) (V)":"1.0","Military":"N","Vsup (+) Maximum (V)":"7.0","JED...

1141 Bytes - 16:35:28, 16 November 2024